对于一个整型变量,多线程访问,到底需不需要互斥锁?

时间:2010-09-06

来源:互联网

作者: rain_fish 发布时间: 2010-09-06

作者: ecjtubaowp 发布时间: 2010-09-06

作者: liwangli1983 发布时间: 2010-09-06

作者: net_robber 发布时间: 2010-09-06

啥意思?

作者: rain_fish 发布时间: 2010-09-06

作者: rain_fish 发布时间: 2010-09-06

作者: hellioncu 发布时间: 2010-09-06

作者: sepnic 发布时间: 2010-09-06

字节对齐上的整型变量在读取和写入时都是原子操作。

字节对齐即,可以被4整除的地址。

最新的P4 CPU.非内存对齐也是原子操作。

http://bbs.chinaunix.net/thread-1777237-1-4.html

作者: zhangsuozhu 发布时间: 2010-09-06

作者: tajial 发布时间: 2010-09-06

- 从Intel486 processor开始,以下的基本内存操作是原子的:

- • Reading or writing a byte(一个字节的读写)

- • Reading or writing a word aligned on a 16-bit boundary(对齐到16位边界的字的读写)

- • Reading or writing a doubleword aligned on a 32-bit boundary(对齐到32位边界的双字的读写)

-

- 从Pentium processor开始,除了之前支持的原子操作外又新增了以下原子操作:

- • Reading or writing a quadword aligned on a 64-bit boundary(对齐到64位边界的四字的读写)

- • 16-bit accesses to uncached memory locations that fit within a 32-bit data bus(未缓存且在32位数据总线范围之内的内存地址的访问)

-

- 从P6 family processors开始,除了之前支持的原子操作又新增了以下原子操作:

- • Unaligned 16-, 32-, and 64-bit accesses to cached memory that fit within a cache line(对单个cache line中缓存地址的未对齐的16/32/64位访问)

-

- 那么哪些操作是非原子的呢?

- Accesses to cacheable memory that are split across bus widths, cache lines, and

- page boundaries are not guaranteed to be atomic by the Intel Core 2 Duo, Intel®

- Atom™, Intel Core Duo, Pentium M, Pentium 4, Intel Xeon, P6 family, Pentium, and

- Intel486 processors.(说点简单点,那些被总线带宽、cache line以及page大小给分隔开了的内存地址的访问不是原子的,你如果想保证这些操作是原子的,你就得求助于机制(2),对总线发出相应的控制信号才行)。

-

- 一个需要注意的是尽管从P6 family开始对非对齐的一些读写操作已经提供了原子性保障,但是非对齐访问时非常影响性能的,一般需要尽量避免。当然了,对于一般的程序员来说不需要太担心这个,因为大部分编译器会自动帮你完成内存对齐。

作者: zhangsuozhu 发布时间: 2010-09-06

热门阅读

-

office 2019专业增强版最新2021版激活秘钥/序列号/激活码推荐 附激活工具

office 2019专业增强版最新2021版激活秘钥/序列号/激活码推荐 附激活工具

阅读:74

-

如何安装mysql8.0

如何安装mysql8.0

阅读:31

-

Word快速设置标题样式步骤详解

Word快速设置标题样式步骤详解

阅读:28

-

20+道必知必会的Vue面试题(附答案解析)

20+道必知必会的Vue面试题(附答案解析)

阅读:37

-

HTML如何制作表单

HTML如何制作表单

阅读:22

-

百词斩可以改天数吗?当然可以,4个步骤轻松修改天数!

百词斩可以改天数吗?当然可以,4个步骤轻松修改天数!

阅读:31

-

ET文件格式和XLS格式文件之间如何转化?

ET文件格式和XLS格式文件之间如何转化?

阅读:24

-

react和vue的区别及优缺点是什么

react和vue的区别及优缺点是什么

阅读:121

-

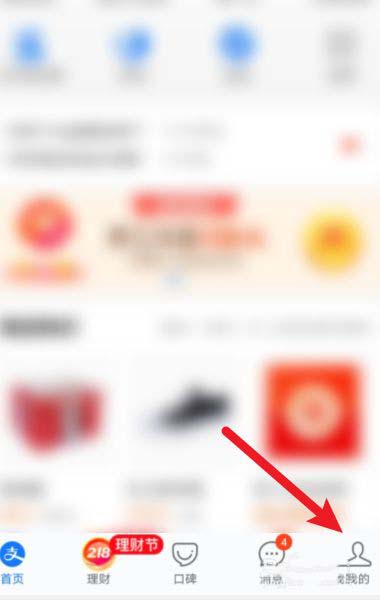

支付宝人脸识别如何关闭?

支付宝人脸识别如何关闭?

阅读:21

-

腾讯微云怎么修改照片或视频备份路径?

腾讯微云怎么修改照片或视频备份路径?

阅读:28